LA MEMOIRE VIVE

L

a mémoire vive est la principale mémoire du PC. Toutes les instructions devant être traitées par le processeur y transitent. Sans cette mémoire, le fonctionnement même de l’ordinateur est impossible, le PC refusant de démarrer. Le montant de la mémoire vive a une grande importance sur le fonctionnement efficace de l’ordinateur. Une PC ne disposant pas d’au moins 16 mégaoctets (16Mo) sera incapable de faire fonctionner correctement Windows 95. Pour beaucoup, seul 32 Mo permet un usage correct d’un ordinateur destiné à la bureautique sous Win 95.La quantité de mémoire peut généralement être augmentée facilement. Pour cela, il convient de tenir compte du type de mémoire utilisée, de la carte-mère et des disponibilités des fournisseurs. De plus, si l’on désire passer la mémoire de 4 à 16Mo, le coût n’est pas de 12Mo, mais de 16Mo. En effet, en ce cas, la mémoire existante ne peut être étendue, mais doit être remplacée.

La façon dont est disposé la mémoire dans votre PC dépend beaucoup la génération de ce dernier. Il est rare que la mémoire soir composée de barrettes SIMM ou DIMM indépendantes les unes des autre. En effet, le bus d’adressage du CPU fixe le nombre de barrettes devant être utilisées simultanément. Par exemple, un Pentium possèdent un bus d’adressage de 64 bits. Ainsi, 2 barrettes de 32 bits ou 8 barrettes de 8 bits devront être utilisées simultanément. En fait, les barrettes de 8 bits ne sont plus utilisées sur les machines Pentium (à moins d’utiliser un adaptateur spécial).

L’ensemble des supports devant être adressés simultanément s’appelle une Bank. Un PC actuel propose généralement entre 2 et 4 Bank, numérotées à partir de 0. L’usage de celle-ci est régis par un certain nombre de règles.

De plus veillez à toujours vérifier dans le manuel de la carte-mère quelles sont les combinaisons de mémoires possibles. Et même si ledit manuel vous autorise à placer de la mémoire EDO dans une Bank, et de la FPM dans une autre, méfiez-vous. Ca marche très bien dans Windows 3.11, ca fait sauter la Registry sous 95 et enfin ça provoque de superbe crash dump sous NT (C’est du vécu).

Prenez garde a ne jamais tenir une barrette de mémoire par les contacts (dorés ou argentés), cela pourrait en altérer la qualité. Attention à l’électricité statique, la mémoire est bien l’élément le plus sensible à ce genre de contrainte. Le port d’un bracelet anti-statique n’est pas requis, il suffit de vous mettre à terre en touchant un élément métallique.

Lors de l’insertion d’une barrette, commencez par en repérer le bon sens. Un de ses côtés possède une encoche, qui sert de détrompeur. La barrette, inclinée sous un angle d’environ 45°, doit pouvoir s’insérer quasiment tout seul dans le support. Une fois bien au fond, il ne vous reste plus qu’à la redresser jusqu'à ce qu’un double déclic se fasse entendre.

Vous avez peut-être constaté que toutes les barrettes ne sont pas désignées de la même façon dans les différents catalogues publicitaires. En effet en parle parfois de barrettes 8 bits ou 9 bits, de 32 bits ou 36 bits. En fait, il s’agit de barrettes avec contrôle de parité. En effet, la mémoire DRAM est très fragile et doit être rafraîchie très souvent. Il arrive que l’un des transistors ou des condensateurs souffre d’un léger dysfonctionnement et perde la valeur stockée. Ce type de panne peut être permanent, ou se produire de temps à autre (problème électrique, microcoupure, ....). Le résultat est lui aussi variable, le PC peut planter net ou continuer comme si de rien n’était. Contrairement aux apparences, le second cas est le plus sournois, tout semble parfaitement aller et le fichier que vous venez de sauver est corrompu.

Une barrette avec contrôle de parité ne permet pas de corriger les erreurs, elle se contente de les annoncer. En ce cas, un message d’erreur du type "ON BOARD PARITY ERROR ADDR (HEX)= 0CFF" apparaît à l'écran. C'est assez proche du "Game Over", cela sous-entend que vous avez perdu la partie et que vous pouvez rebooter votre PC. Pour arriver à ce résultat, un bit de parité est ajouté pour 8 bits de données.

Il existe deux protocoles de contrôle de parité:

| Parité paire | Parité impaire | |

| Etape 1 | Le bit de parité est défini à 1, ou ON, si les bits

sous contrôle contiennent un nombre pair de 1 Si les bits contrôlés contiennent un nombre impair de 1, le bit de parité est défini à 0, ou OFF |

Le bit de parité est défini à 1, ou ON, si les bits

sous contrôle contiennent un nombre impair de 1 Si les bits contrôlés contiennent un nombre pair de 1, le bit de parité est défini à 0, ou OFF |

| Etape 2 | Le bit de parité et les 8 bits correspondant sont écrits dans la mémoire DRAM | Le bit de parité et les 8 bits correspondant sont écrits dans la mémoire DRAM |

| Etape 3 | Juste avant que les données soient envoyées au

processeur, elles sont interceptées par le circuit de parité. Si le circuit de parité voit un nombre impair de 1, les données sont considérées comme valide. Le bit de parité est alors détruit et les 8 bits restants sont passés au processeur. Si le circuit de parité détecte un nombre impair de 1, les données sont considérées comme invalides et une erreur de parité est générée. |

Juste avant que les données soient envoyées au

processeur, elles sont interceptées par le circuit de parité. Si le circuit de parité voit un nombre pair de 1, les données sont considérées comme valide. Le bit de parité est alors détruit et les 8 bits restants sont passés au processeur. Si le circuit de parité détecte un nombre impair de 1, les données sont considérées comme invalide et une erreur de parité est générée. |

Et si y'a deux bits qui sont perdus ...? Paraît que c'est aussi rare que les fautes de protection sous Windows 95. En tout cas, ce système ne fonctionne effectivement pas si un nombre pair de bits est perdu. A l'origine, le contrôle de parité était effectué par un chip nommé 74LS280 parity generator/checker.

Certains constructeurs n'ont pas hésité à fabriquer de faux circuits de parité, très peu coûteux. Un tel type de circuit génère le bit de parité au moment où les données sont envoyées au processeur. Si le contrôle est de type IMPAIR, un 1 est généré, dans le cas de la parité PAIR, c'est un 0. Ainsi, le contrôle de parité affirmera toujours que les données sont valides. Un tel circuit ne sert donc strictement à rien et se rapproche dangereusement de l'arnaque pur et simple.

La signification de l'abréviation ECC est Error Checking and Correction. A la différence de la mémoire avec contrôle de parité, la mémoire ECC permet la détection, mais aussi la correction d'erreur. Pour arriver à ce résultat, le nombre de bits destiné à corriger la mémoire est bien plus élevé. Cette mémoire ne peut être utilisée que sur des cartes mères équipées d'un chipset adéquat. Attention, peu d'entre eux supportent cette fonctionnalité, vérifiez bien ce point avant tout achat. Ces fonctionnalités plus qu'intéressantes la positionnent sur un segment de marché haut de gamme. En effet, son coût actuel n'en permet pas un emploi généralisé dans les PC domestiques ou bas de gamme.

Suivant le type de contrôleur de mémoire, il est possible de corriger 1, 2, 3 ou même 4 bits invalides.

Désormais dépassée , elle équipait la plupart des 386 et des 486. Disposant d'un temps d'accès de 70ns ou 60ns, cette dernière offre des performances inacceptables pour toute machine dont la vitesse du bus est supérieure à 66 Mhz ( Pentium, Pentium Pro, ...). Afin d'augmenter sa vitesse, elle corrige un problème usuel des mémoires de type DRAM. En effet lorsqu'on recherche une donnée, un signal électrique charge les lignes afin de trouver d'abord la ligne, ensuite la colonne ( une valeur étant stockée à ce croisement ). Le fait que ces lignes électriques ne se stabilisent pas immédiatement provoque un délai de temps de réponse. Les mémoires FPM ( Fast Page Mode ) corrigent ce problème en supposant que la prochaine requête va concerner la prochaine colonne de la même ligne. Ce qui est souvent le cas. Ainsi, le temps d'attente de recherche d'une ligne est nul. Le gain de vitesse ainsi obtenu était très net par rapport à la DRAM standard. Malgré ses faibles performances et son âge avancé, cette mémoire reste utilisable dans la plupart des PC.

Ce type de mémoire, qui se présente généralement sous la forme d'une barrette SIMM de 72pins, est utilisable par tous les PC de la gamme Pentium dotés d'un chipset Triton ou plus récent. Le principe utilisé par la mémoire FPM perd toute efficacité si le processeur travaille trop vite ( vitesses supérieures à 33Mhz ). C'est là qu'intervient la mémoire EDO. En effet, elle intègre un jeu de cellules mémoire à la sortie qui contient les données qui vont être demandées par le processeur. Il s'agit, en quelque sorte, d'une mémoire cache intégrée à la mémoire vive. Ce type de mémoire a généralement un temps d'accès de 60 ou 50ns. Pour des raisons de performances et stabilité, la mémoire EDO et FPM ne devraient pas être utilisées simultanément.

Au-dessus de 66Mhz, il sera préférable d'utiliser de la Burst EDORAM ( mode rafale ). Ce type de mémoire sous-entend que le processeur va demander les données stockées aux prochaines adresses. Elle en charge alors quatre automatiquement en un cycle d'horloge. Concurrente de la mémoire SRAM, il semblerait que la partie ne soit pas gagnée d'avance.

Depuis l'apparition des processeurs DX2, il existe une différence de vitesse entre le processeur et la carte mère. La mémoire étant placée sur cette dernière, il n'est pas rare qu'elle soit jusqu'à 3 fois plus lente que le CPU. La SDRAM présente l'avantage de fonctionner à la même fréquence que le processeur. Ainsi, elle est à même d'anticiper ses demandes et d'offrir un temps de réponse minimum. De plus, elle travaille en mode burst, ce qui en augmente encore le débit.

Le mode Burst (rafale)est de type "5-1-1-1", soit 5 cycles d'horloge pour lire/écrire la première donnée, 1 cycle pour la seconde, 1 cycle pour la troisième et enfin un cycle pour la quatrième. Une mémoire de type EDO sera "5-2-2-2". En effet, elle est asynchrone et utilise donc deux cycles pour chaque donnée.

| Type | Cycles de lecture/écriture | Nbre de cycles total |

| FPM | 5-3-3-3 | 14 |

| EDO | 5-2-2-2 | 11 |

| SDRAM | 5-1-1-1 | 8 |

Elle peut fonctionner à une fréquence supérieure à 100 Mhz. Elles atteignent un débit maximum de 640 Mbps. Lors de l'achat d'une mémoire de ce type, il faut veiller à en choisir le modèle correct. En effet, elle est disponible en barrettes DIMM à 5 ou à 3.3V. Un autre point fort de cet type de mémoire est qu'il est possible de lire plusieurs banks simultanément. Cette possibilité permet de fournir un flot de données continu au processeur.

Proposée par la société MoSys, il s'agit d'une mémoire SDRAM améliorée de manière à permettre un accès rapide avec une large bande passante. La mémoire MDRAM est synchronisée à 333 Mhz et peut fournir un débit de 666 Mbytes/s. On peut imaginer celle-ci comme un ensemble de blocs de mémoire de 32 ko indépendants. Chacun disposant d'une interface propre de 32 bits. Ils sont reliés ensemble à l'aide d'un bus commun. L'interface externe n'est qu'une version améliorée du bus interne, disposant d'un buffer permettant de relativiser les différences de débit. Afin d'éviter tout problème de perte de données, il fait aussi fonction de répétiteur. Les adresses des différents blocs sont gérées à l'intérieur de la banque elle-même. Ce procédé permet d'en masquer la complexité aux éléments externes, rendant ainsi son adressage simple. De multiples banques peuvent être assemblées en cascade de façon à en augmenter la capacité (en anglais, on parle de map). Cette mémoire fonctionne à 5 ou 3.3 V.

Afin d'augmenter le débit de la mémoire, la mémoire DDR-SRAM est capable de transférer des données sue les courbes montantes et descendantes du signal (comme l'EIDE). Cette technologie est appelée Double Data Rate (DDR) permet des transferts de l'ordre de 1.03Go/s. La mémoire de type DDR-SRAM ou SRAM II a été acceptée comme standard par huit grands fabricants (Samsung, Nec, Toshiba, ...)

Le standard SLDRAM est un nouveau standard ouvert, libre de royalties proposé par SyncLink, un consortium regroupant les principaux constructeurs de DRAM. Ce standard est très proche des mémoires de type RDRAM proposées par Rambus. La SLDRAM propose un double bus de données à 200Mhz, 16 bits et orienté paquets. Il permettrait des débits de l'ordre de 800 Mo par secondes.

La demande actuelle en mémoire s'accroît de manière exponentielle (quand je pense que j'étais très fier de mon Atari gonflé à 2Mo il n'y a pas si longtemps). L'utilisation des mémoires actuelles en grand nombre nécessite l'usage de cache coûteux afin de réduire les temps de réponse. Il est aussi possible d'augmenter la fréquence d'horloge de la mémoire, à l'instar de la SDRAM. Ce procédé, s'il offre des débits intéressants, à ses limites. En effet, la complexité de ces composants en est un frein. Chaque composant ajouté à ses propres temps de latence, qui, additionnés, ne permettent pas d'atteindre des fréquences extrêmement élevées. De plus, la mémoire est reliée en parallèle au contrôleur, ce qui en limite le débit et génère de problème de synchronisation. Ceux-ci ne permettent pas de pousser la fréquence.

La société Rambus propose désormais une nouvelle technologie permettant de passer outre ces limitations, et cela à faible coût. Il convient avant tout de savoir que Rambus ne fabrique pas de composants, cette société ne se charge que de la partie développement. Ces spécifications sont ensuite reprises par les grands fabricants de composants mémoires, qui se chargent de fabriquer et de commercialiser cette technologie. Cette technologie est appelée Rambus, et utilise des composants mémoires RDRAM (Rambus Direct RAM).

Rambus propose une toute nouvelle approche de la mémoire actuelle. Pour eux, la mémoire n'est pas seulement une barrette ou une puce, mais un système complet. C'est effectivement le seul moyen d'obtenir une mémoire efficace et cohérente. La technologie Rambus est proche des réseaux à topologie bus, ou des chaînes SCSI. A la base se trouve un contrôleur chargé de piloter l'ensemble. Il alimente un bus à haute vitesse, où la mémoire et connectée en série. Le tout étant terminé par une résistance, le terminateur. Tout cela permet d'atteindre une fréquence de 800Mhz et des débits calculés de l'ordre de 1.6 Go par secondes. Les informations de contrôles sont transmises via des lignes dédiées, séparées des lignes de données. Les données sont émises sur les crêtes ascendantes et descendantes du signal d'horloge.

Cette technologie a d'ores et déjà été prévue pour des utilisations très diverses. Les fonctions intégrées de gestion d'énergie la destine aux ordinateurs de tables comme aux ordinateurs portables. Un 9ème bit par byte est déjà prévu pour un éventuel contrôle de parité, très apprécié sur les serveurs réseaux.

En résumé, cette nouvelle technologie devrait rapidement s'imposer sur le marché. De très nombreux constructeurs ont déjà annoncé leur intérêt prononcé pour la mémoire Rambus. Récemment, AMD a annoncé le support de la mémoire MDRAM dans son futur processeur K7, prévu pour l'automne 1999.

Le contrôleur Direct Rambus est le composant chargé de gérer le bus mémoire du même nom. Cet élément peut être intégré dans le chipset, le processeur ou encore dans le contrôleur graphique. Il sert alors de liaison entre le composant logique et le bus mémoire Rambus. Ses fonctions comprennent la génération des requêtes, le contrôle du flot de données, ainsi que la gestion des différents états de la mémoire. Il est possible de placer jusqu'à quatre contrôleurs de ce type dans un simple composant logique.

Le contrôleur Direct Rambus est en réalité constitué de deux éléments distincts: le Rambus ASIC Cell (RAC) et le Rambus Memory Controller (RMC). Le RAC est cadencé à la même fréquence d'horloge que le bus proprement dit, qui peut atteindre 400 Mhz. Il a pour fonction de servir d'interface physique et électrique pour le bus. Il est composé de mémoire cache (buffers) et de multiplexeurs, comme par exemple celui chargé de donner la fréquence du bus. Sa forme est celle d'un circuit BGA (Ball Grid Array), et utilise 76 connecteurs.

Le RMC est le contrôleur logique du bus. Il agit comme interface entre le circuit logique et le RAC. Il reçoit les requête mémoire du circuit logique et les transmet au bus, après les avoir traduites selon le protocole Direct Rambus.

Le bus est en fait une liaison électrique entre le contrôleur Rambus et les composants mémoires proprement dits (les RDRAMs). Les transferts sont basés sur 30 signaux à haute vitesse. Les données sont transférées sur les deux crêtes du signal (ascendantes et descendantes), qui est cadencé à 400Mhz. Cela permet des taux de transferts de l'ordre de 800 Mbits par secondes et par ligne.

Le bus se décompose comme suit: 16/18 signaux pour les données, 3 pour le contrôle des lignes et enfin 5 pour les colonnes. En effet, la désignation d'une zone spécifique de la mémoire se fait toujours en spécifiant un croisement de ligne et colonnes. On peut comparer ce procédé à la circulation dans une ville comme New-York. Votre destination pourrait ainsi être au croisement de la 5ème avenue et de la 112ème rue, sauf que dans la mémoire, le désagréable chauffeur de taxi est remplacé par un contrôleur indifférent. Chacun de ces trois éléments fonctionne de manière indépendante. Les lignes de données sont bidirectionnelles, elles sont ainsi utilisées pour amener et renvoyer une valeur de la mémoire. Les lignes d'adressages (lignes et colonnes) sont unidirectionnelles. Elles sont envoyées par le contrôleur en direction de la mémoire. Le fait d'utiliser des lignes distinctes pour les données et l'adressage permet d'obtenir un rendement nettement supérieur à la mémoire traditionnelle. La raison pour laquelle le nombre de signaux pour les données peut être de 16 ou de 18 est simple. Rambus a en effet prévu un bit de parité pour 8 bits de données, mais il peut aussi être utilisé pour des données.

Le bus Direct Rambus est terminé à son extrémité libre par une résistance 1,8V, le contrôleur se chargeant de terminer l'autre extrémité. Cette terminaison absorbe les signaux, évitant ainsi toute réflexion qui pourrait diminuer la qualité du signal originel.

Les données sont transmises le long du bus sous forme de paquets, tel les protocoles réseaux les plus courants (TCP/IP, ...). Ce procédé présente de nombreux avantages. En effet, il permet de diminuer le nombre de lignes nécessaires pour la communication des données. Ainsi, il est possible de concevoir des bus de très petite taille, réduisant ainsi les pertes de données. Enfin, le nombre de bits prévu pour l'adressage a été volontairement calculé large. Ainsi, le nombre standard de bit d'adresse pour la ligne est de 24 bits, et 40 bits pour la colonne, le tout étant placé dans le paquet proprement dit. Ce choix permet de gérer une mémoire totale allant jusqu'à 1 Go sans devoir ajouter un quelconque signal de contrôle. En effet, toutes les adresses pouvant être spécifiées dans le paquet de base. Cela offre un système évolutif sans remettre en cause les acquis, ou sans devoir modifier la norme de base, la compatibilité est désormais garantie.

Les barrettes RIMM (Rambus Inline Memory Module) sont basées sur la forme des barrettes DIMM. La comparaison s'arrête là, car si elles sont mécaniquement compatibles, il n'en va pas de même du point de vue électrique. Le support utilisé dispose de 168 contacts.

A la différence d'une barrette EDO, chacun des différents composants mémoire (RDRAM) n'est pas accessible directement. En effet, un unique bus commençant d'un côté de la barrette, relie un à un les RDRAM jusqu'à son autre extrémité. Ainsi, il n'est pas possible de laisser un support RDRAM libre, il interromprait la chaîne. A cet effet, des circuits ne contenant pas de mémoire ont été développés. Appelé "continuity modules", ils ne servent qu'à prolonger la chaîne. Il faut toujours garder en tête que ces composants ne sont accessibles que les un après les autres, un peu comme une chaîne SCSI. Ce système est parfaitement visible sur la barrette RIMM proprement dite. On y voit parfaitement les différents câbles entrer à une extrémité, ensuite relier un à un les composants, puis ressortir à l'autre extrémité.

Les barrettes RIMM existent en version simple ou double face. Dans le premier cas, elles peuvent supporter jusqu'à huit RDRAM, alors que ce nombre atteint seize dans le second cas.

Un bus Rambus peut supporter au maximum 32 composants RDRAMs, que leur capacité soit de 64, 128 ou encore 256 Mbits. Cela autorise une capacité globale de l'ordre de 256, 512 ou 1 Go, selon le type de composant utilisé. Lorsque des mémoires standards (EDO, FPM, ...), les supports sont regroupés en banks, celles-ci devant être remplies dans leur intégralité. Dans le cas de mémoire Rambus, la notion de banque est abandonnée au profit du bus. Ce dernier ne doit en aucun cas être interrompu, il commence au contrôleur et se termine à la résistance finale. Vous ne désirez placer qu'une unique barrette ? Pas de problème, mais il vous faudra compléter les autres slots du bus à l'aide de "continuity modules". Ces barrettes supplémentaires ne contiendront pas de mémoire, mais garantiront la continuité et l'intégrité du bus.

Si 32 composants RDRAMs ne vous suffisent plus, il est tant d'abandonner les produits Microsoft et de passer sur Linux. Non, c'est pour rire, vous pouvez ajouter des composants nommés répétiteurs. Ceux-ci ont pour rôle d'amplifier et de garantir la qualité du signal sur une plus longue distance. Il vous sera ainsi possible d'augmenter le nombre de composants, sous-entendu de barrettes RIMMs, supportés. Un répétiteur vous permet de gérer au total 6 barrettes RIMMs(64 composants), deux répétiteurs porteront ce chiffre à 12 barrettes RIMMs (128 composants). Si cela ne vous suffit toujours pas à faire tourner votre application maison, envoyez un dossier de candidature chez Bill Gates (il cherche des développeurs pour son futur NT 6).

Les modules Rambus Direct RAM (RDRAM) sont en fait les "puces" de mémoire proprement dit. Leur fonction est de stocker les données, et de répondre aux requêtes émises par le contrôleur Rambus. On y distingue deux composants: l'interface logique et le "noyau".

Le rôle de l'interface logique est de servir d'intermédiaire entre les paquets émis à 400Mhz sur le bus et le noyau (mémoire CMOS à 100Mhz). La taille des données est ainsi convertie afin de pouvoir être lues par ces deux éléments.

Le noyau contient la mémoire, ainsi que les contrôles logiques (lignes, colonnes). Un circuit RDRAM de 64 Mbits est composé de 32 banks de 128 bits chacune. A la différence des mémoires SDRAM, les banks RDRAM sont dépendantes les unes des autres. Ce système offre l'avantage de diminuer le nombre de composants de contrôle, ceux-ci sont partagés par plusieurs banques. Cela permet de placer plus de mémoire sur une surface réduite, tout en diminuant les coûts de fabrications. En contrepartie, le nombre de bank pouvant être ouvertes simultanément est réduit.

Un des points fort de la technologie est la gestion de l'énergie. Ce type de mémoire a été conçu dès le départ pour des applications nécessitant de faible consommation (ordinateurs portables, ...). Les composants RDRAMs nécessitent une tension de 2.5V, alors que le bus n'utilise que 1.8V.

Quatre modes d'opération ont étés prévus: Active, Standby, Nap et PowerDown.

| Active | Dans ce mode, le module RDRAM est instantanément prêt à répondre à une requête. Ce mode est le plus gros consommateur d'énergie des quatre. Par contre, à la différence des mémoires usuelles, seul le module qui est lu consomme beaucoup d'énergie, le reste de la bank passe ne basse consommation |

Standby |

A la fin d'une transaction, les modules RDRAM basculent automatiquement en mode Standby. De même, lorsque l'adresse d'un module à été décodée, ce dernier reste en mode Active, alors que le reste de la bank passe en Standby. |

Nap |

Nap en traduction littérale signifie petit sommeil, mignon non ? Ce mode consomme moins que le Standby, mais le temps pour passer en mode Active est plus long. La très faible consommation de ce mode le rend tut de même très intéressant. |

PowerDown |

Ici, pas besoin de donner top de précision. La mémoire n'est plus alimentée, donc une consommation nulle. Par contre, le temps de réveil est en conséquence |

La forme sous laquelle se présente la mémoire est un élément aussi important que la technologie utilisée. En effet, chaque carte-mère propose un certain nombre de supports à un format donné. C'est donc cet élément qui définit les possibilités d'extension de la mémoire. Généralement, les supports présents permettent d'accéder aux formats les plus courants du moment. Mais si vous voulez absolument acquérir le dernier cri en matière de mémoire, il est souvent nécessaire d'envisager aussi un changement de carte-mère.

Les barrettes SIP (Single In-Line Package) sont tombées en désuétude depuis un certain temps déjà. Elles se présentaient sous forme d’une barrette avec des broches à insérer dans un compartiment récepteur. Ces barrettes avaient soit une valeur de 256ko, soit de 1Mo. Leur seule utilisation actuelle est celle de mémoire pour certaines cartes graphiques. Leur fragilité est l'une des raisons de son faible succès, en effet, une patte pouvait être trop facilement pliée ou cassée.

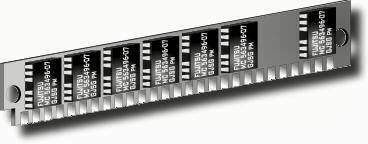

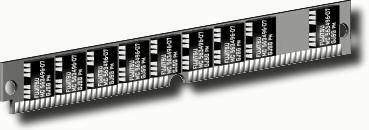

La mémoire SIMM (Single In-Line Memory Module) de 8 bits se présente sous la forme d’une barrette d'environ 8.5 cm de long, sur laquelle sont fixés des composants électroniques. Elle est aussi souvent appelée barrette SIMM 30 pins. On les place dans des connecteurs groupés par deux (386SX) ou quatre (dès le 386DX), généralement les carte-mères comportent deux bank (bank 0 et bank 1). Une bank doit impérativement être utilisée dans son intégralité. Ces barrettes peuvent avoir une valeur de 256ko, 1Mo ou 4Mo. Ainsi pour avoir 20 Mo de mémoire, on place quatre barrettes de 4Mo dans la bank 0 et quatre barrettes de 1Mo dans la bank 1. Il faut veiller à toujours utiliser des barrettes de même vitesse, généralement entre 70 nanosecondes et 60 ns. Chaque barrette a une encoche dans l'angle inférieur gauche qui sert de détrompeur, évitant ainsi de la monter à l'envers.

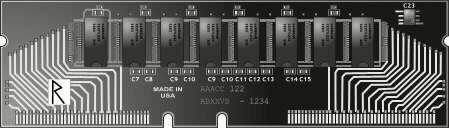

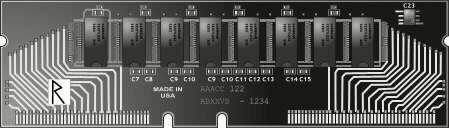

Les barrettes SIMM 32bits / 72 pins

La mémoire SIMM de 32 bits (appelée aussi SIMM 72 pins) se présente aussi sous la forme d’une barrette, mais plus longue que les 8 bits (environ 10.5 cm). Au niveau des valeurs, les SIMM 32 bits disponibles sont de 1Mo, 2Mo, 4Mo, 8Mo, 16Mo, 32Mo et 64Mo. Actuellement, des études sont menées par différents constructeurs (Siemens entre autres) afin de construire une barrette de 256 Mo. Ces barrettes sont surtout utilisées dans les Pentiums, ainsi que sur les carte-mères 486 récentes. Ce format est pourtant relativement ancien, car certains constructeurs (IBM, Compaq, ... ) l'utilisaient déjà il y a plusieurs années comme format propriétaire dans leur PC. Méfiez-vous de ces barrettes propriétaires, elles ne fonctionnent généralement que dans les machines de la même marque. Les barrettes SIMM 32 ont deux détrompeurs, une encoche dans le coin inférieur gauche (comme les SIMM 8 bits) et une encoche arrondie au centre de la barrette. Il n'est pas rare de trouver ces barrettes avec des composants sur les deux faces .

Les barrettes DIMM

Les barrettes DIMM (Dual In-Line Memory Module) sont désormais supportées par la plupart des PC récents. Actuellement utilisées uniquement pour la mémoire SDRAM, elles se présentent sous la forme d'une barrette longue de 13,3 cm. Adaptée aux Pentiums, elles sont composées de 64 bits (72 avec contrôle de parité), on les appelle communément DIMM 168 pins. Les barrettes SIMM32 ont 72 connecteurs sur chaque face, mais ils sont liés entre eux. Ainsi, le connecteur 1 de la première face est équivalent au premier de l'autre face. A l'inverse, une barrette DIMM a 84 connecteurs sur chaque face, mais chacun est indépendant. Ces barrettes sont disponibles en 5 et en 3.3V, et en version buffered ou unbuffered. Le format le plus courant reste le 3.3V unbuffered, mais par acquit de conscience, vérifiez tout de même le manuel de votre carte-mère.

Les barrettes RIMM

Les barrettes RIMM (Rambus In-Line Memory Module) sont nées de la spécification Rambus, crée par la société du même nom. Si elles sont mécaniquement compatibles avec les barrettes DIMM, elles ne le sont pas électriquement. Inutile donc d'essayer de les placer dans un support DIMM et d'en espérer le bon fonctionnement. Ces barrettes présentes la particularité d'être lue en ligne. En effet, les données entrant sur un côté de la barrette, traverses les composants mémoires et ressortent de l'autre côté. La notion de bank, chère aux DIMM, n'est pas applicable aux RIMM. Les barrettes sont toujours groupées par trois, mais des "continuity modules" peuvent être utilisées. Peu coûteuses, ces barrettes sans mémoire ont pour unique fonction d'assurer la continuité du bus de données.

Les circuits DIP

Les Circuits DIP (Dual In-Line Package) ne sont actuellement plus utilisés comme mémoire vive, mais plutôt comme mémoire cache. Ils sont facilement reconnaissables à leur double lignée de broches. Lorsqu'ils faisaient office de mémoire vive, une carte mémoire insérée dans un slot propriétaire ou une carte-mère particulière était nécessaire. En effet, leur faible capacité (64ko ou 256 ko) obligeait à en disposer un nombre considérable pour atteindre un minimum de 640ko de mémoire vive. Ce type de circuit est aussi utilisé pour les BIOS. Ils existent sous forme de PROM, EPROM, EEPROM. Une encoche arrondie sur la face supérieure permet d'insérer le circuit dans le bon sens. En effet, une marque identique est présente sur le support.

Ces modules ne sont utilisés que pour augmenter la mémoire cache des PC récents. Ils se présentent sous la forme d'une petite barrette SIMM. Il en existe différentes tailles en fonction de vos besoins. Certains intègrent une mémoire Tag-Ram, nécessaires selon la taille de mémoire cache finale désirée. Attention, toutes les cartes mères n'acceptent pas forcément ce type de modules, les plus anciennes n'acceptent que des circuits DIP.